We współpracy z KAMAMI.pl przygotowaliśmy szkolenia mające na celu zapoznanie uczestników z podstawami implementacji sprzętowych projektów w układach FPGA na przykładzie nowoczesnych układów z rodziny MAX10 (Altera/Intel), zastosowanych w zestawie maXimator.

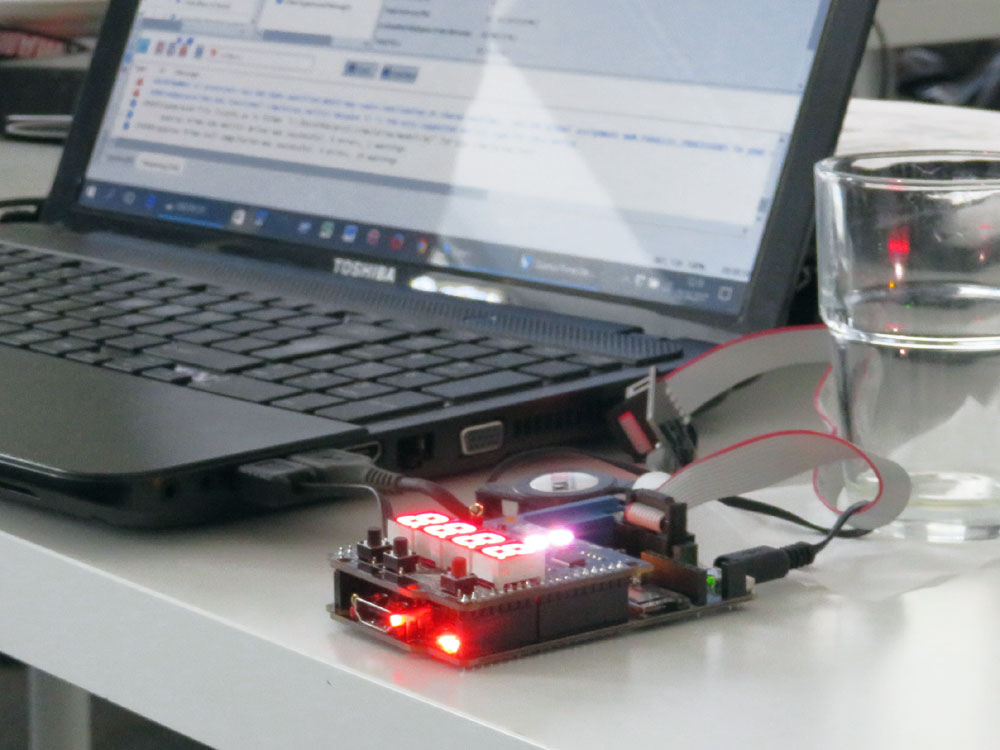

Podczas warsztatów uczestnicy mogli zrealizować pełne ścieżki implementacji kilku prostych projektów cyfrowych – od opisu, przez syntezę, symulację, aż do wykonania w fizycznym układzie scalonym FPGA. Projekty realizowane były za pomocą języka opisu sprzętu (HDL) Verilog.

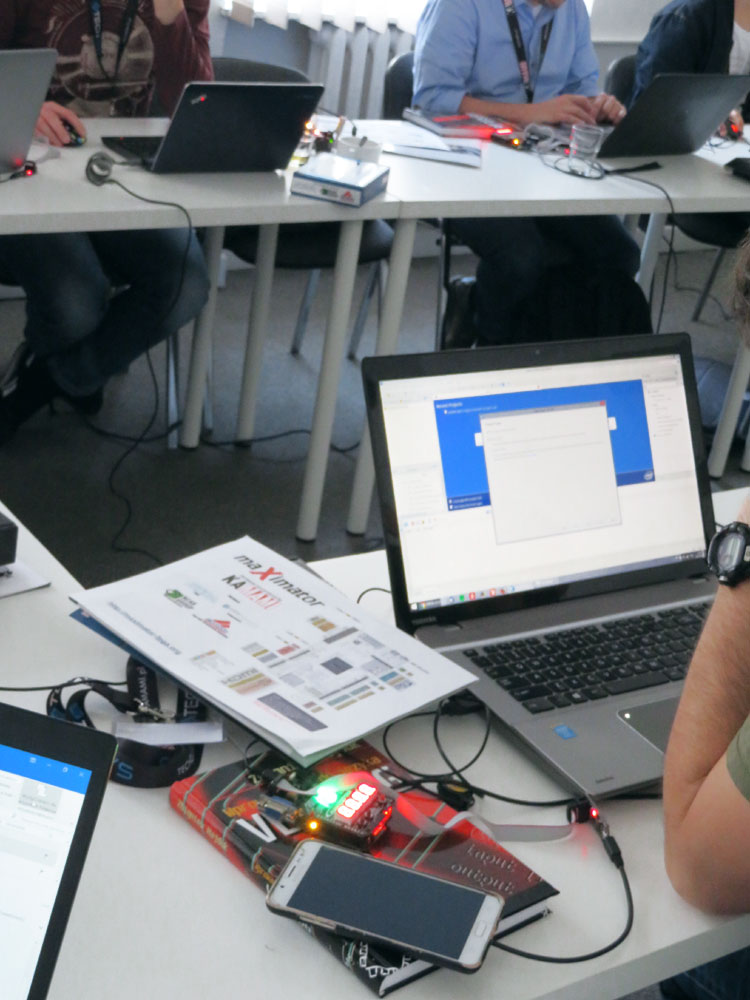

Każdy z uczestników otrzymał po zakończeniu szkolenia książkę „Wprowadzenie do języka Verilog” (autor: Zbigniew Hajduk).

Poniżej przedstawiamy krótką fotorelację z kolejnych warsztatów, które odbyły się 5 kwietnia br. w Warszawie.