- KRAKÓW

28 listopada 2018

08:30 - 16:00 - POZNAŃ

29 listopada 2018

08:30 - 16:00 - ŁÓDŹ

30 listopada 2018

08:30 - 16:00

Akademickie warsztaty FPGA – ZYBO Video Workshop 2018

UWAGA: warsztaty są prowadzone w języku angielskim

Cel szkolenia

Uczestnicy warsztatów zapoznają się w praktyce z możliwościami pakietu narzędziowego Xilinx Vivado, sprzętowej platformy Digilent Video Processing oraz sposobami zastosowania w projektach gotowych modułów IP (w tym filtra Sobela), które – z myślą o obróbce sygnałów wideo – zostały przygotowane przez firmy Xilinx i Digilent.

Szkolenie jest przeznaczone dla kadry naukowo-technicznej uczelni, inżynierów projektujących lub chcących projektować w FPGA i SoC oraz studentów chcących poznać od strony praktycznej nowoczesne metody implementacji i realizacji projektów embedded real-time.

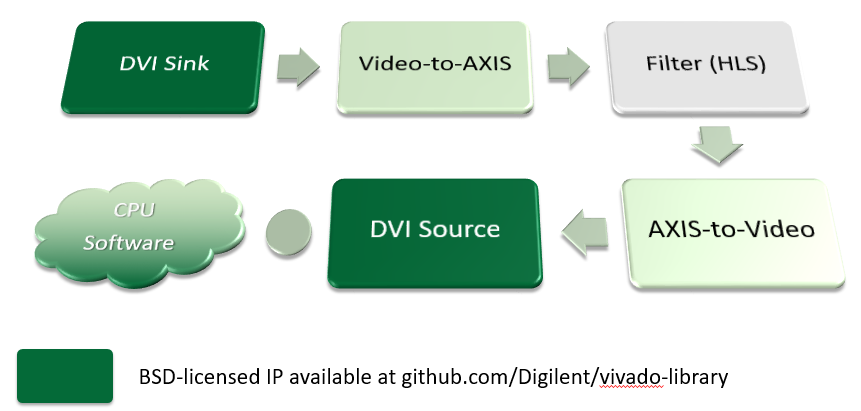

Narzędzia wykorzystywane podczas warsztatów

Uproszczony schemat blokowy projektu implementowanego i testowanego podczas warsztatów.

Wymagane przygotowanie słuchaczy

Znajomość podstawowych zagadnień techniki cyfrowej, FPGA, VHDL i C++. Ćwiczenia będą wykonywane na zestawach Digilent ZYBO Z7, monitorach udostępnionych przez organizatorów oraz własnych komputerach uczestników.

Uczestnicy warsztatów muszą się wyposażyć w komputer:

- z wyjściem HDMI;

- z systemem Windows 7 lub wyższym;

- z zainstalowanym oprogramowaniem Vivado 2017.4 – WAŻNE! Prosimy upewnić się, że zainstalowane są również SDK i HLS oraz pliki konfiguracyjne płytki dla dla HLS. Wystarczy licencja na pakiet sieciowy;

Monitory, zestawy ZYBO i kable niezbędne do wykonania ćwiczeń zapewniają organizatorzy.

Program szkolenia

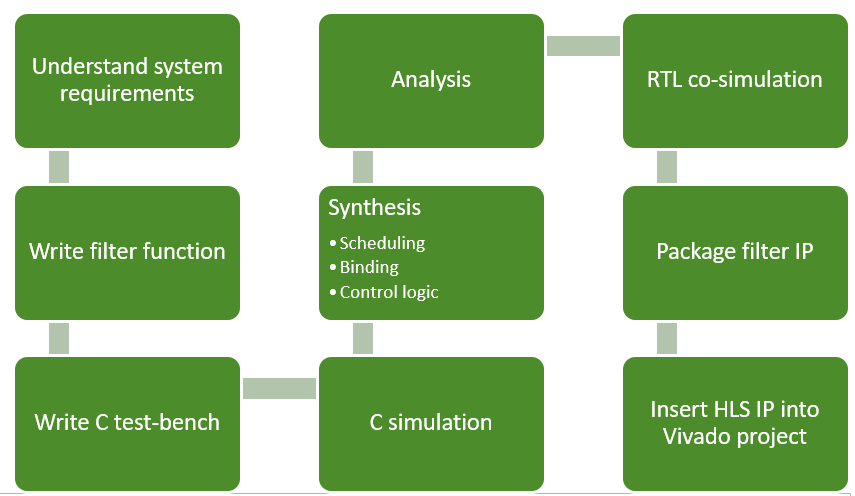

Zadania realizowane podczas warsztatów pokazano na diagramie poniżej.

Uczestnicy zapoznają się od strony praktycznej z zagadnieniami wysokopoziomowej syntezy logicznej (HLS – High Level Synthesis) w aplikacjach czasu rzeczywistego, implementacją algorytmów realizowanych sprzętowo na układach System-on-Chip (SoC), nauczą się także metod korzystania z IP core’ów we własnych projektach, poznają zasady symulacji i debugowania projektów implementowanych w SoC.

NABÓR ZAKOŃCZONY

Kod szkolenia DIGIFPGA02

Czas trwania 6 h

Szkolenie rozpocznie się w godzinach porannych – szczegóły przesyłane będą wszystkim osobom zakwalifikowanym do udziału.

Partnerzy

Współpraca organizacyjna: